13 – 16 November 2017 Renaissance Kuala Lumpur Hotel www.apmc2017.com

## 75 GHz InP DHBT Power Amplifier Based on Two-Stacked Transistors

<u>Michele Squartecchia</u><sup>#</sup>, Virginio Midili<sup>#</sup>, Tom K. Johansen<sup>#</sup>, Jean-Yves Dupuy<sup>\*</sup>, Virginie Nodjiadjim<sup>\*</sup>, Muriel Riet<sup>\*</sup>, Agnieszka Konczykowska<sup>\*</sup>

# Department of Electrical Engineering, Technical University of Denmark\* III-V Lab (joint lab of Nokia Bell Labs, Thales, and CEA-Leti), France

# Outline

- Introduction and motivation

- Stacked-transistor configuration

- InP technology at III-V Lab

- Two-stacked transistor power cell

- Two-stage 8-way power amplifier

- Ongoing and future works

- Conclusions

## **Introduction and motivation**

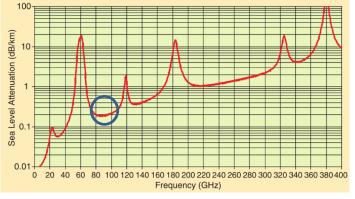

• The W-band (75-110 GHz) has very favorable features

Low atmospheric attenuation

Emerging applications:

ullet

▶ ....

- Satellite and back-haul wireless links at E-band (71-76 GHz and 81-86 GHz)

- Automotive radars (77 GHz)

- Radio astronomy and earth observation (94 GHz)

Microwaves for the Internet of Things

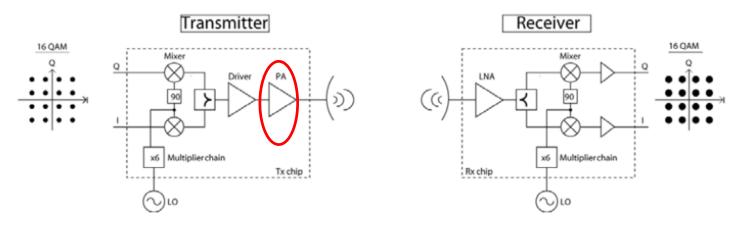

#### **NEED FOR POWER AMPLIFIERS**

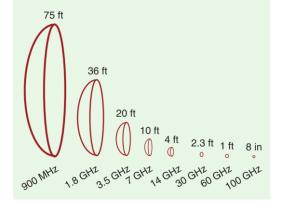

Small system size

• W-band power amplifiers design challenges

Ex: Wireless data link

1) High output power; 2) High gain; 3) Efficiency; 4) Good linearity

• High frequencies of operation  $\rightarrow$  device downscaling  $\rightarrow$  low breakdown voltages

$\implies P_{Tx} \cdot f^2 \approx const$

Investigation on topologies to overcome these limitations

# Outline

- Introduction and motivation

- Stacked-transistor configuration

- InP technology at III-V Lab

- Two-stacked transistor power cell

- Two-stage 8-way power amplifier

- Ongoing and future works

- Conclusions

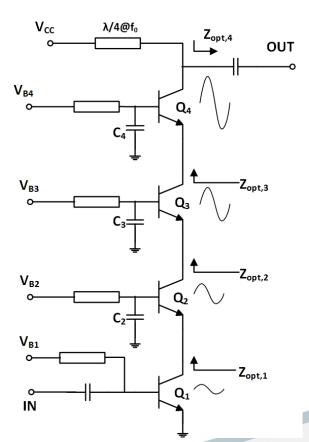

## **Stacked-transistor configuration**

- The overall output voltage swing is *n* times higher than a single device

- Approximately the same current flows through all the transistors

- Output power and gain are potentially *n* times higher than a single device

- Design constraints:

- Voltage equally shared

- Phase alignment

- Microwaves for the Internet of Things

- Interstage matching

# Outline

- Introduction and motivation

- Stacked-transistor configuration

- InP technology at III-V Lab

- Two-stacked transistor power cell

- Two-stage 8-way power amplifier

- Ongoing and future works

- Conclusions

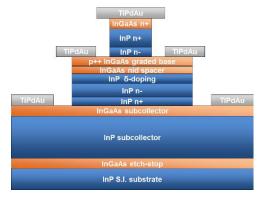

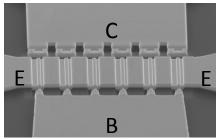

## InP technology at III-V Lab

#### Double Heterojunction Bipolar Transistors (DHBTs)

Single-finger device

| 2 |  |

|---|--|

|   |  |

|   |  |

Multifinger device

Emitter width:  $W_E = 0.7 \ \mu m$

Available emitter lengths:  $L_E = 5\mu m$ ,  $7\mu m$  and  $10\mu m$

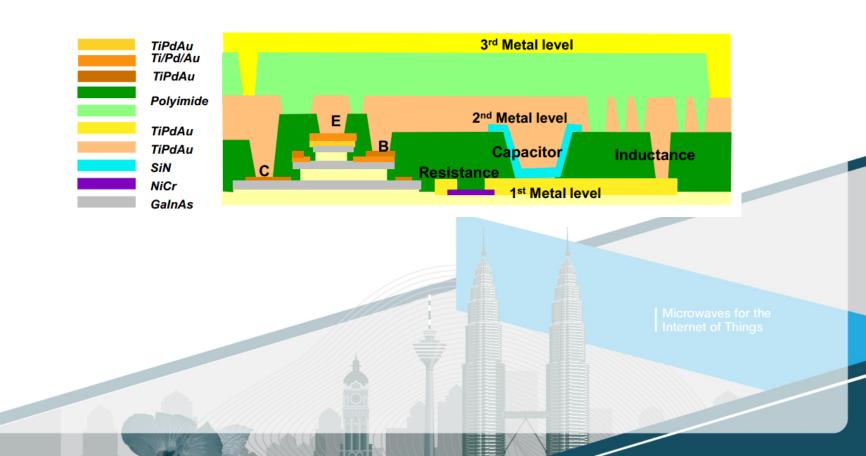

## High-speed mixed-signal optimized process (aka SHARC)

- β > 25

- $f_T \approx 400 \text{ GHz}$

- •f<sub>max</sub> > 350 GHz

- BVceo ≈ 5 V

#### Power optimized process (aka SAND)

- Thicker collector

- β > 25

- f<sub>⊤</sub> ≈ 270 GHz

- f<sub>max</sub> > 420 GHz

- Microwaves for the Internet of Things

- BVceo ≈ 7 V

## InP technology at III-V Lab

#### Layer stack

# Outline

- Introduction and motivation

- Stacked-transistor configuration

- InP technology at III-V Lab

- Two-stacked transistor power cell

- Two-stage 8-way power amplifier

- Ongoing and future works

- Conclusions

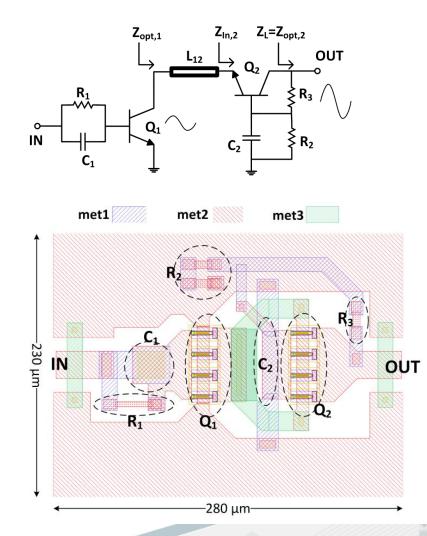

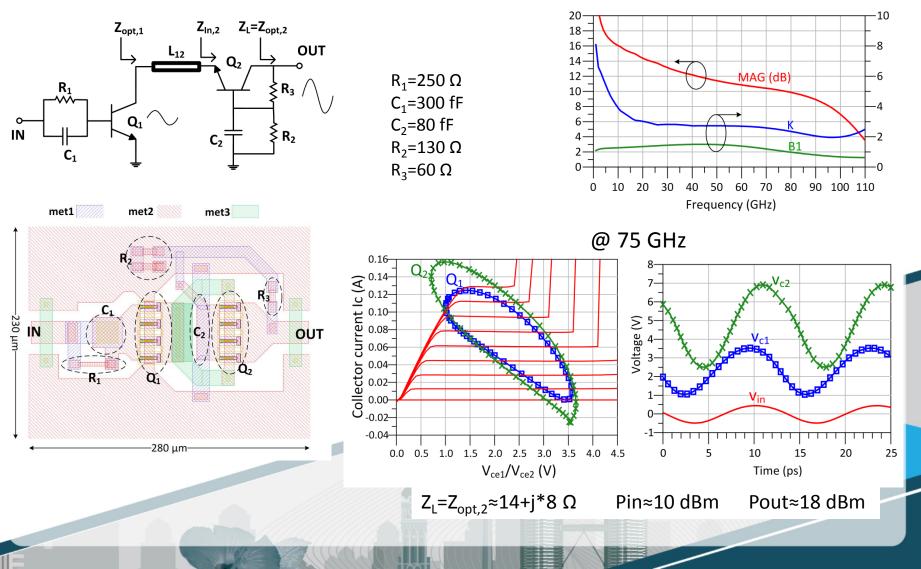

#### **Two-stacked transistor power cell**

- Four-finger devices (4×0,7×10 μm<sup>2</sup>)

- Q1-Q2  $\rightarrow$  UCSD model

- Class A:  $V_{ce1}=V_{ce2}=2.4$  V and  $I_{c1}\approx I_{c2}=60$ mA

- R<sub>1</sub>-C<sub>1</sub> for biasing and low frequency stability

- R<sub>2</sub>-R<sub>3</sub> for self-bias and improved stability

- L<sub>12</sub>: physical connection and interstage matching

#### **Two-stacked transistor power cell**

#### EM-circuit co-simulation and optimization

#### **Two-stacked transistor power cell**

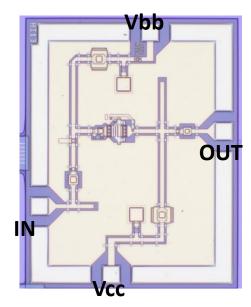

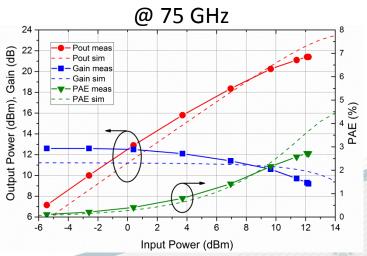

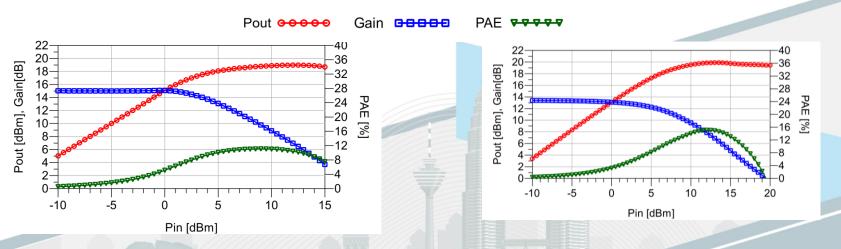

#### Matched power cell (SHARC process realization)

Bias settings Vbb=1.4 V

Ibb=1.9 mA

Vcc=4.9 V Icc=84 mA

Output Power (dBm)

Power sweep measurement setup

# Outline

- Introduction and motivation

- Stacked-transistor configuration

- InP technology at III-V Lab

- Two-stacked transistor power cell

- Two-stage 8-way power amplifier

- Ongoing and future works

- Conclusions

Renaissance Kuala Lumpur Hotel

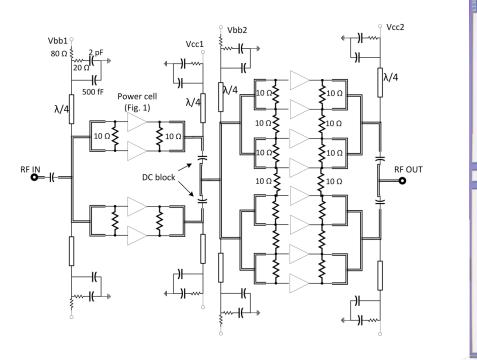

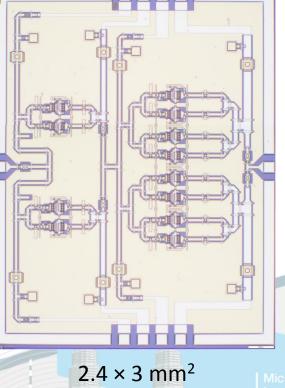

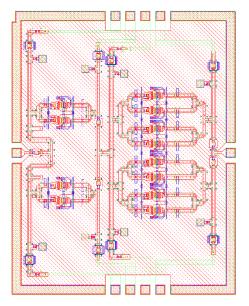

### **Two-stage 8-way power amplifier**

Microwaves for the

**Bias settings**

Vbb1=1.7 V

Vcc1=4 V

Vbb1=2 V Ibb1=8 mA

Vcc2=4,5 V

lcc2=340 mA

Ibb1=4,1 mA

lcc1=172 mA

Renaissance Kuala Lumpur Hotel

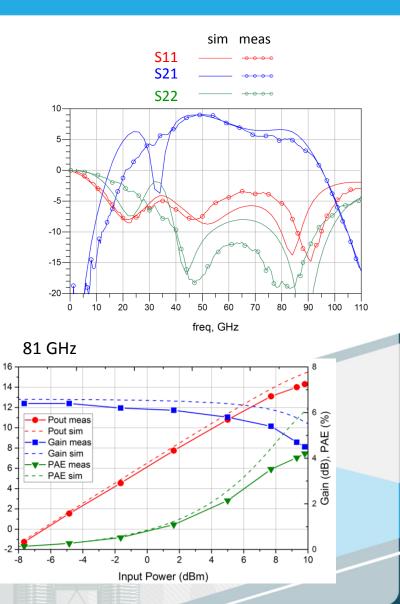

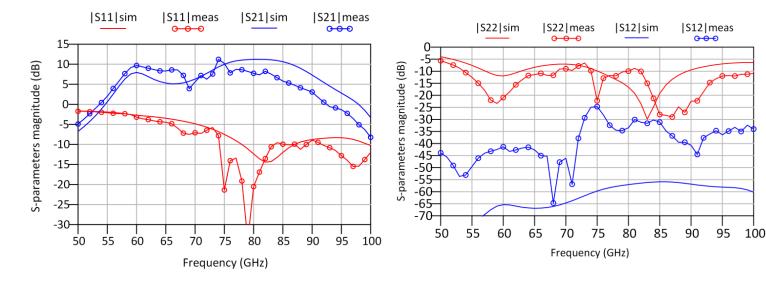

#### **Two-stage 8-way power amplifier**

- Gain  $\approx$  12 dB

- P<sub>out,1dB</sub> ≈ 18 dBm

- P<sub>sat</sub> > <mark>21</mark> dBm

# Outline

- Introduction and motivation

- Stacked-transistor configuration

- InP technology at III-V Lab

- Two-stacked transistor power cell

- Two-stage 8-way power amplifier

- Ongoing and future works

- Summary and conclusions

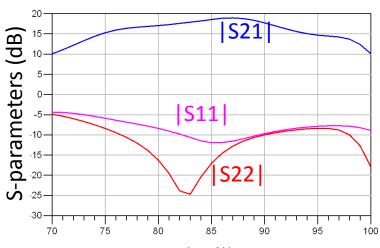

## **Ongoing and future works**

# Simulation results on power optimized process SAND

- Gain ≈ 18 dB

- P<sub>out,1dB</sub> ≈ 22 dBm

- P<sub>sat</sub> > 24 dBm

freq, GHz

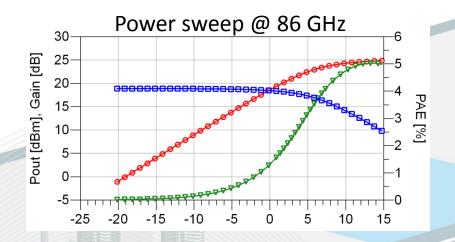

## **Ongoing and future works**

# Three-stacked transistor

#### Preliminary results (SAND process)

#### Simulated power sweep at 86 GHz

#### Four-stacked transistor

# Outline

- Introduction and motivation

- Stacked-transistor configuration

- InP technology at III-V Lab

- Two-stacked transistor power cell

- Two-stage 8-way power amplifier

- Ongoing and future works

- Summary and conclusions

## **Summary and conclusions**

- This work represents an attempt to extend the stacked-transistor concept to InP DHBT technology in order to get higher performances in terms of output power, gain and efficiency.

- A two-stage eight-way 75 GHz power amplifier based on two-stacked transistors has been designed and tested.

G ≈ 12 dB, P<sub>out,1dB</sub> ≈ 18 dBm and P<sub>sat</sub> > 21 dBm have been obtained experimentally.

- Better performances are expected from a power optimized process currently under development.

- Three- and four-stacked power cells under investigation with promising preliminary results.

13 – 16 November 2017 Renaissance Kuala Lumpur Hotel

#### Acknowledgments

Renaissance Kuala Lumpur Hotel

**Acknowledgments**

## Thank you for your attention!